Device for winding the readings of electric meters

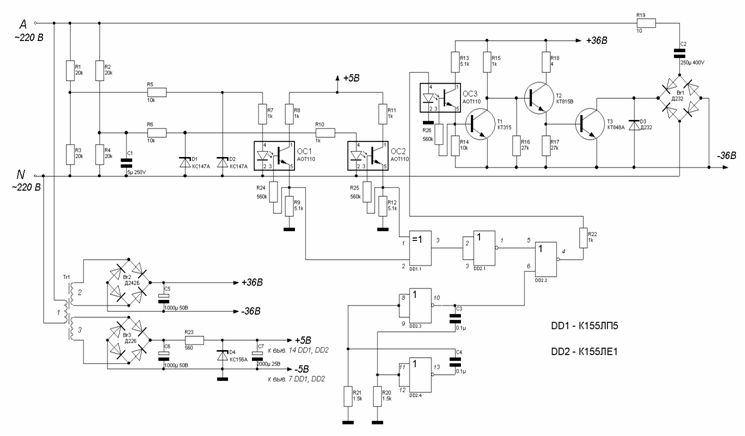

Fig.1. Electric schematic diagram

The device is designed to rewind indications of induction electric meters without changing their switching circuits. With regard to electronic and electronic-mechanical counters, the construction of which is incapable of counting down the readings, the device allows you to completely stop the recording to the level of the reactive power of the generator. With the elements indicated on the diagram, the device is designed for a rated voltage of 220 V and the winding power is approximately 2 kW. The use of other elements allows you to increase the power accordingly. The device, assembled according to the proposed scheme, is simply inserted into the socket, and the counter begins to count in the opposite direction. All wiring remains intact. Earthing is not necessary.

Schematic diagram of the device

Schematic diagram is shown in Fig. The main elements of the device are the integrator, which is the resistor bridge R1-R4 and the capacitor C1, the pulse driver (zener diodes D1, D2 and resistors R5, R6), the logic node (DD1.1, DD2.1, DD2.2 elements), the clock generator (DD2.3, DD2.4), the amplifier (T1, T2), the output stage (C2, T3, Br1) and the power supply unit on the transformer Tr1. The integrator is designed to isolate from the mains voltage signals that synchronize the operation of the logical node. These are rectangular TTL level pulses at the inputs 1 and 2 of the DD1.1 element. The front of the signal at input 1 DD1.1 coincides with the beginning of the positive half-wave of the mains voltage, and the decline - with the beginning of the negative half-wave. The signal front at input 2 DD1.1 coincides with the onset of the positive half-wave of the mains voltage integral, and the decay coincides with the onset of the negative half-wave. Thus, these signals are rectangular pulses synchronized by the network and displaced in phase relative to each other by an angle p / 2. The signal corresponding to the mains voltage is removed from the resistor divider R1, R3, limited to a level of 5 V by using a resistor R5 and a zener diode D2, then through a galvanic isolation on the optocoupler OC1 is fed to the logical node. Similarly, a signal corresponding to the network voltage integral is formed. The process of integration is provided by the processes of charge and discharge of the capacitor C1. The logic node serves to generate control signals for the powerful key transistor T3 of the output stage. The control algorithm is synchronized with the output signals of the integrator. Based on the analysis of these signals, an output control signal is generated at the output 4 of the DD2.2 element. At the necessary times, the logic node modulates the output signal with the master oscillator signal, providing high-frequency power consumption. To ensure the impulse process of charging the storage capacitor C2 is the master oscillator on the logic elements DD2.3 and DD2.4. It generates pulses with a frequency of 2 kHz with an amplitude of 5 V. The frequency of the signal at the output of the generator, and the duty cycle of the pulses are determined by the parameters of the timing chains C3-R20 and C4-R21. These parameters can be selected during tuning to ensure the greatest error in the metering of the electrical energy consumed by the device. The control signal of the output stage through the galvanic isolation on the optocoupler OC3 is fed to the input of a two-stage amplifier on the transistors T1 and T2. The main purpose of this amplifier is full opening with the introduction of the output stage in the saturation mode of the transistor T3 and reliable locking of it at the time points determined by the logical node. Only the saturation and full-closing input will allow the T3 to function in the harsh operating conditions of the output stage. If you do not ensure reliable full opening and closing of T3, and in a minimum time, then it breaks down from overheating in a few seconds. The power supply is built according to the classical scheme. The need for two power channels is dictated by the feature of the output stage mode. Ensure a reliable opening of the T3 is possible only with a voltage of at least 12V, and to supply the chips requires a stabilized voltage of 5V. At the same time, it is only possible to consider the negative pole of the 5-volt output as a common wire. It must not be earthed or connected to network wires. The main requirement for the power supply is the ability to provide a current of up to 2 A at the output of 36 V. This is necessary for the input of a powerful key transistor of the output stage to saturation in the open state. Otherwise, it will dissipate large power, and it will fail.

Parts and construction

Microcircuits can be used any: 155, 133, 156 and other series. It is not recommended to use microchips based on MOSFET structures, since they are more susceptible to interference from the operation of a powerful key stage. The key transistor T3 must be installed on the radiator with an area of at least 200 cm2. For the transistor T2 a radiator with an area of at least 50 cm2 is used. For safety reasons, the metal housing of the device should not be used as radiators. The storage capacitor C2 can only be non-polar. The use of an electrolytic capacitor is not allowed. The capacitor must be rated for a voltage of at least 400V. Resistors: R1 - R4, R15 type MLT-2; R18, R19 - wire with a power of at least 10 W; Other resistors of the MLT-0.25 type. Transformer Tr1 - any power about 100 W with two separate secondary windings. The voltage of the winding 2 must be 24 - 26. In, the voltage of the winding 3 must be 4 - 5 V. The main requirement is that the winding 2 should be rated for a current of 2 - 3 A. The winding 3 is low-power, the current consumption from it will not exceed 50 mA. The device as a whole is assembled in a casing. It is very convenient (especially for conspiracy purposes) to use for this purpose a housing from a household voltage regulator, which in the recent past was widely used for powering lamp TVs.

Adjustment.

Be careful when adjusting the circuit! Remember that not all of the low-voltage part of the circuit has a galvanic isolation from the electrical network! It is not recommended to use the metal case of the device as the radiator for the output transistor. The use of fuses is a must! The storage capacitor operates in the limit mode, so before turning on the device, it must be placed in a sturdy metal casing. The use of an electrolytic (oxide) capacitor is not allowed! The low-voltage power supply unit is checked separately from other modules. It must provide a current of at least 2 A at the output of 36 V, as well as 5 V for powering the control system. The integrator is tested by a two-beam oscilloscope. To do this, the common oscilloscope wire is connected to the neutral power line (N), the first channel wire is connected to the connection point of the resistors R1 and R3, and the second channel wire to the connection point R2 and R4. On the screen you should see two sinusoids with a frequency of 50 Hz and an amplitude of about 150 V each, displaced along the time axis by an angle of p / 2. Further, the presence of signals at the outputs of the limiters is checked by connecting the oscilloscope parallel to the zener diodes D1 and D2. To do this, connect the common oscilloscope wire to the network point N. The signals must have a regular rectangular shape, a frequency of 50 Hz, an amplitude of about 5 V, and must also be offset by an angle of p / 2 along the time axis. A rise and fall of pulses is allowed for not more than 1 ms. If the phase shift of the signals differs from p / 2, then it is corrected by selecting capacitor C1. The steepness of the front and the decay of the pulses can be changed by selecting the resistances of the resistors R5 and R6. These resistances must be at least 8 kΩ, otherwise the signal level limiters will affect the quality of the integration process, which will eventually lead to an overload of the output stage transistor. Then set up the generator, having disconnected the power part of the circuit from the mains. The generator must generate pulses with an amplitude of 5 V and a frequency of about 2 kHz. The pulse width is approximately 1/1. If necessary, capacitors C3, C4 or resistors R20, R21 are selected for this purpose. The logical node does not require a correct installation. It is advisable to verify with the help of an oscilloscope that at the inputs 1 and 2 of the element DD1.1 there are periodic signals of a rectangular shape displaced relative to each other along the time axis by an angle p / 2. At the output 4 DD2.2, bursts of 2 kHz pulses are periodically generated every 10 ms, the duration of each burst is 5 ms.

Setting the output stage is to set the current base of the transistor T3 at a level of at least 1.5 -2 A. This is necessary to saturate this transistor in the open state. For tuning, it is recommended to disconnect the output stage with the amplifier from the logic node (disconnect the resistor R22 from the output of the DD2.2 element), and control the cascade by supplying a voltage of +5 V to the disconnected contact of the resistor R22 directly from the power unit. Instead of the capacitor C1, a n-load in the form of a 100 W incandescent lamp is temporarily included. The current of the base T3 is set by selecting the resistance of the resistor R18. For this, it may be necessary to select the R13 and R15 amplifiers. After ignition of the optocoupler OC3, the current of the base of the transistor T3 should decrease almost to zero (several μA). Such tuning provides the most favorable thermal mode of operation of a powerful key transistor of the output stage.

After setting up all the elements, restore all connections in the circuit and check the operation of the circuit assembly. It is recommended to perform the first switching with a reduced value of capacitance C2 up to about 1 μF. After switching on the device, allow it to run for several minutes, paying special attention to the temperature regime of the key transistor. If everything is in order - you can increase the capacity of the capacitor C2. Increase capacity to the nominal value is recommended in several stages, each time checking the temperature regime. The power of the winding depends primarily on the capacitance of the capacitor C2. To increase power, you need a larger capacitor. The limiting value of the capacitance is determined by the magnitude of the impulse current of the charge. Its magnitude can be judged by connecting the oscilloscope parallel to the resistor R19. For transistors KT848A, it should not exceed 20 A. If you want to increase the power of the winding, you will have to use more powerful transistors, as well as diodes Br1. But it is better to use another circuit with an output stage on four transistors. It is not recommended to use too much power of the winding. As a rule, 1 kW is enough. If the device works in conjunction with other consumers, the meter will subtract the power of the device from their power, but the wiring will be loaded with reactive power. This must be taken into account so as not to disable the wiring.

Comments

Commenting on, remember that the content and tone of your message can hurt the feelings of real people, show respect and tolerance to your interlocutors even if you do not share their opinion, your behavior in the conditions of freedom of expression and anonymity provided by the Internet, changes Not only virtual, but also the real world. All comments are hidden from the index, spam is controlled.